[논리설계] Combinational Logic 및 예제

디지털 논리회로는 크게 Combinational circuit과 Sequential circuit으로 나눌 수 있다.

Combinational circuit이란 출력값이 입력값에만 의존하여 결정되는 회로를 말하며,

Sequential circuit이란 회로 내부에 상태(state)를 저장할 수 있어 현재의 입력값뿐만 아니라 과거의 입력값들에도 출력이 의존하는 회로를 말한다. 회로의 상태는 레지스터(register)를 통해 구현된다.

Combinational Logic Example: Calendar Subsystem

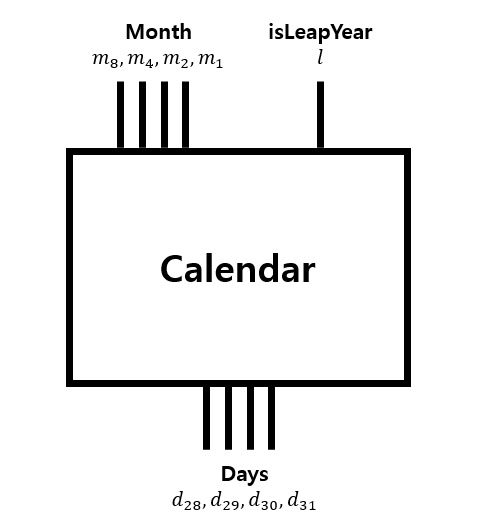

Combinational Logic의 예시로, 달이 주어졌을 때 해당 달에 며칠이 있는지 출력하는 회로를 생각해 보자.

이 회로는 현재 무슨 달인지와 윤년인지 여부를 입력으로 받아, 해당 월에 대응하는 날의 수를 출력하는 회로이다. 무슨 달인지에 관한 입력은 1부터 12 사이의 십진수를 이진수로 변환해 m8, m4, m2, m1 네 개의 wire로 입력되고, 윤년인지 여부를 나타내는 l은 1(윤년) 또는 0(윤년 아님)의 값으로 입력된다. 이제 이 회로의 내부를 설계해 보자.

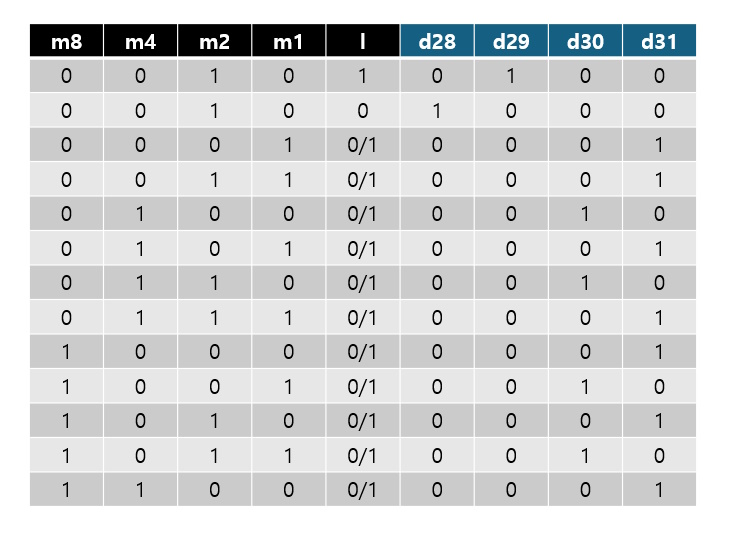

Combinatinoal Logic을 설계하는 데 기본적인 단계는 진리표(Truth Table)를 작성하는 것이다.

위 진리표는 모든 가능한 입력의 조합과 대응하는 출력값을 한 행씩 적은 표이다. 한편 m8=1, m4=1, m2=1, m1=1, l=0과 같이 고려할 필요가 없는 불가능한 입력에 대해서는 ("Don't care"라고 한다.) 진리표에 표시하지 않았는데, 이들에 대해서는 어떤 출력을 내놓아도 상관없기 때문이다. 즉 회로를 설계할 때 불가능한 입력 조합에 대해서는 고려할 필요가 없다.

다음 단계는 진리표를 토대로 논리식을 작성하는 것이다.

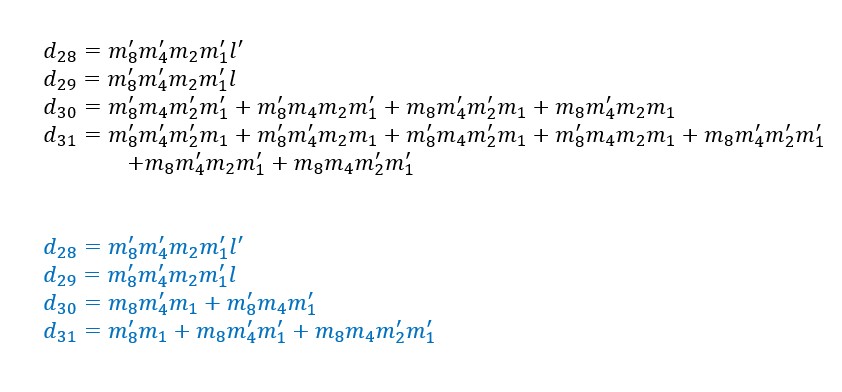

위 사진의 검은 글씨로 작성된 논리식은 진리표의 각 행을 하나의 항으로 기계적으로 옮겨 작성한 것이다. 그러나 이 식은 다소 복잡하다. 따라서 Boolean algebra의 성질들을 사용해 논리식을 간소화하는 작업이 필요하다. 예를 들어, m8m4m2m1 + m8m4m2m1'은 m8m4m2로 간소화할 수 있다.

가장 간략한 형태는 아닐 수 있지만, 대략적으로 간소화를 거친 논리식을 위 사진의 파란 글씨로 나타냈다. 이제 이 논리식에 따라 wire와 논리 게이트를 연결하면

참고로, 논리식의 간소화는 입력 개수가 적은 경우 (일반적으로 5개 이하) Karnaugh map(K-map) 등의 알고리즘을 이용하기도 한다.

Verilog 구현 및 시뮬레이션

추가로, 위의 디지털 논리 회로를 HDL(Hardware Description Language)인 Verilog로 작성하여 보았다.

calendar.v

module calendar(

input wire[3:0] m,

input wire l,

output wire d28,

output wire d29,

output wire d30,

output wire d31

);

assign d28 = (m==2) && (l==0);

assign d29 = (m==2) && (l==1);

assign d30 = 1;

assign d31 = 1;

endmodule

또한 이 module을 test하기 위한 testbench 코드도 작성하였다.

tb_calendar.v

module tb_calendar();

reg [3:0] m; reg l;

wire d28; wire d29; wire d30; wire d31;

calendar u_calendar(

.m (m),

.l (l),

.d28 (d28),

.d29 (d29),

.d30 (d30),

.d31 (d31)

);

initial begin

m = 2; l = 1; #10;

m = 2; l = 0; #10;

m = 1; l = 0; #10;

m = 3; l = 0; #10;

m = 4; l = 0; #10;

m = 5; l = 0; #10;

m = 6; l = 0; #10;

m = 7; l = 0; #10;

m = 8; l = 0; #10;

m = 9; l = 0; #10;

m = 10; l = 0; #10;

m = 11; l = 0; #10;

m = 12; l = 0; #10;

end

endmodule

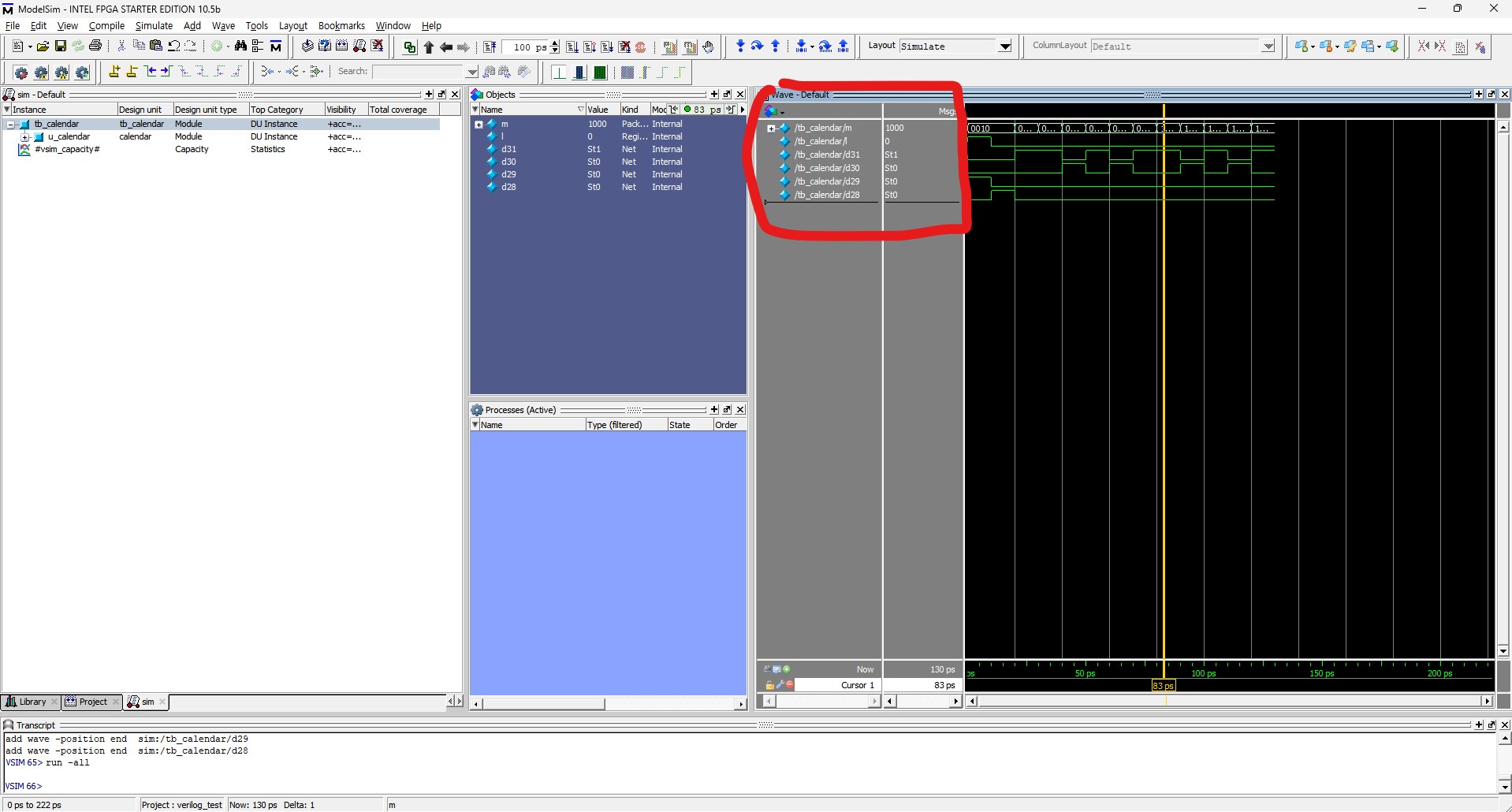

또한 하드웨어 시뮬레이션 도구 ModelSim을 이용하여 위 코드로 구현된 논리회로를 시뮬레이션해 보았다.

위 사진은 시뮬레이션을 실행한 ModelSim 화면이다. 붉은색으로 표시된 영역을 보면 m 레지스터가 1001(9월), l 레지스터가 0(윤년 아님) 의 값을 가질 때 출력 wire 중 d31만 1의 값을 가지는 것을 확인할 수 있다.

이와 같이 간단한 Combinational Logic을 설계, 작성하고 시뮬레이션해 보았다. 다음 포스팅에서는 Sequential Logic의 개념과 간단한 예제 구현을 정리해보도록 하겠다.